# Powerline Communications Analog Front-End

Check for Samples: AFE031

### **FEATURES**

- Integrated Powerline Driver with Thermal and Overcurrent Protection

- Conforms to EN50065-1

- PRIME Certified

- Large Output Swing: 12 V<sub>PP</sub> at 1.5 A (15-V Supply)

- Low Power Consumption:

15 mW (Receive Mode)

- Programmable Tx and Rx Filters

- Supports EN50065 CENELEC Bands A, B, C, D

- Supports FSK, S-FSK, and OFDM

- Supports PRIME, G3, IEC 61334

- Receive Sensitivity: 20 μV<sub>RMS</sub>, Typical

- Programmable Tx and Rx Gain Control

- Four-Wire Serial Peripheral Interface

- Two Integrated Zero Crossing Detectors

- Two-Wire Transceiver Buffer

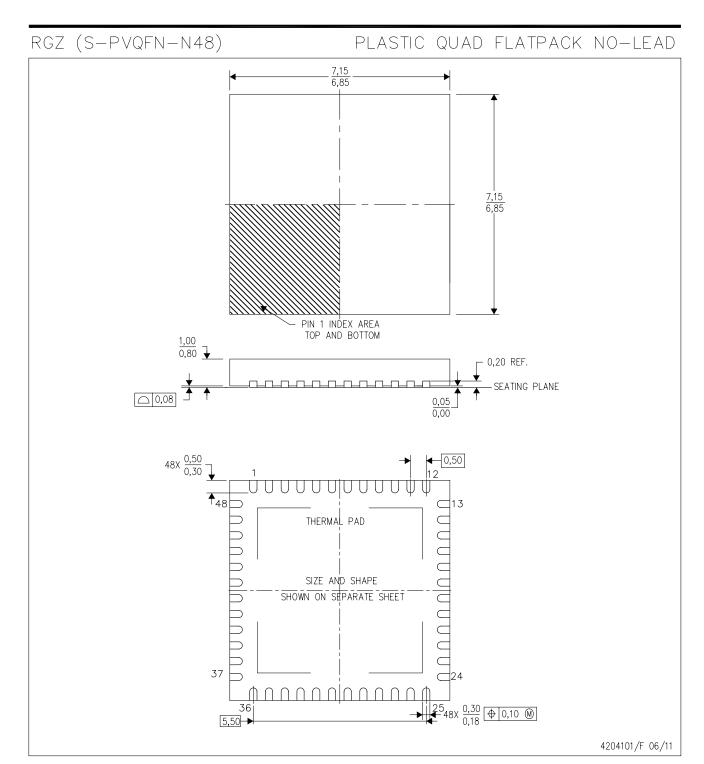

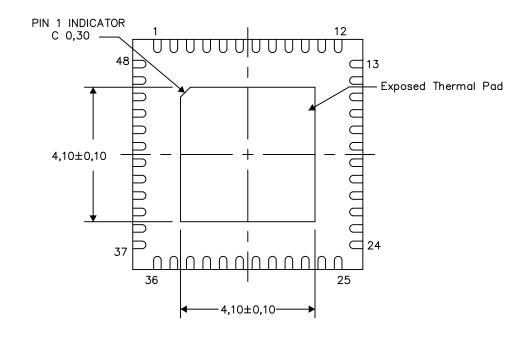

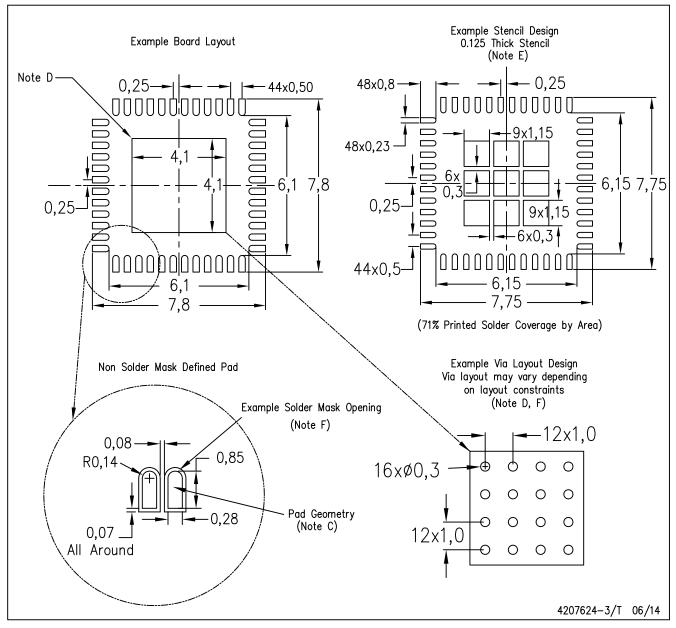

- 48-Pin QFN PowerPAD™ Package

- Extended Junction Temperature Range: -40°C to +125°C

### **APPLICATIONS**

- eMetering

- Lighting

- Solar

- Pilot Wire

### DESCRIPTION

The AFE031 is a low-cost, integrated, powerline communications (PLC) analog front-end (AFE) device that is capable of capacitive- or transformer-coupled connections to the powerline while under the control of a DSP or microcontroller. It is ideal for driving lowimpedance lines that require up to 1.5 A into reactive loads. The integrated receiver is able to detect signals down to  $\bar{20}~\mu V_{RMS}$  and is capable of a wide range of gain options to adapt to varying input signal conditions. This monolithic integrated circuit provides high reliability in demanding powerline communications applications.

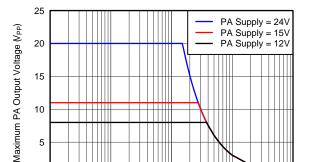

The AFE031 transmit power amplifier operates from a single supply in the range of 7 V to 24 V. At maximum output current, a wide output swing provides a 12- $V_{PP}$  ( $I_{OUT}=1.5$  A) capability with a nominal 15-V supply. The analog and digital signal processing circuitry operates from a single 3.3-V power supply.

The AFE031 is internally protected against overtemperature and short-circuit conditions. It also provides an adjustable current limit. An interrupt output is provided that indicates both current limit and thermal limit. There is also a shutdown pin that can be used to quickly put the device into its lowest power state. Through the four-wire serial peripheral interface, or SPI™, each functional block can be enabled or disabled to optimize power dissipation.

The AFE031 is housed in a thermally-enhanced, surface-mount PowerPAD package (QFN-48). Operation is specified over the extended industrial junction temperature range of -40°C to +125°C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD, C2000 are trademarks of Texas Instruments.

SPI is a trademark of Motorola, Inc.

All other trademarks are the property of their respective owners.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

## PACKAGE/ORDERING INFORMATION(1)

| PRODUCT      | PACKAGE-LEAD    | PACKAGE DESIGNATOR | PACKAGE MARKING |

|--------------|-----------------|--------------------|-----------------|

| AFE031AIRGZT | QFN-48 PowerPAD | RGZ                | AFE031A         |

| AFE031AIRGZR | QFN-48 PowerPAD | RGZ                | AFE031A         |

<sup>(1)</sup> For the most current package and ordering information see the Package Option Addendum at the end of this document, or visit the device product folder at www.ti.com.

## **ABSOLUTE MAXIMUM RATINGS**(1)

Over operating free-air temperature range (unless otherwise noted).

|                                                                                     |                            | VALUE                                   | UNIT |

|-------------------------------------------------------------------------------------|----------------------------|-----------------------------------------|------|

| Supply voltage, PA_V <sub>S</sub>                                                   |                            | +26                                     | V    |

| Signal input terminal,                                                              | Voltage <sup>(2)</sup>     | PA_GND - 0.4 to PA_V <sub>S</sub> + 0.4 | V    |

| pins 18,19                                                                          | Current <sup>(2)</sup>     | ±10                                     | mA   |

| Supply voltage, AV <sub>DD</sub>                                                    |                            | +5.5                                    | V    |

| Signal input terminal,                                                              | Voltage <sup>(2)</sup>     | AGND – 0.4 to AV <sub>DD</sub> + 0.4    | V    |

| pins 13, 15, 16, 21, 23, 24, 25, 28, 32, 34, 35, 38, 39, 46                         | Current <sup>(2)</sup>     | ±10                                     | mA   |

| Signal input terminal, pin 27                                                       | Voltage limit              | ±10                                     | V    |

| Signal input terminal, pin 10                                                       | Current limit              | ±10                                     | mA   |

| Supply voltage, DV <sub>DD</sub>                                                    |                            | +5.5                                    | V    |

| Signal input terminal,                                                              | Voltage <sup>(2)</sup>     | DGND – 0.4 to DV <sub>DD</sub> + 0.4    | V    |

| pins 3, 4, 6, 7, 8                                                                  | Current <sup>(2)</sup>     | ±10                                     | mA   |

| Signal output terminal,<br>pins 5, 9, 14, 17, 20, 22, 26,<br>31, 33, 36, 37, 47, 48 | Current <sup>(2)</sup>     | Continuous                              |      |

| Output short-circuit (PA), pins 4                                                   | 2,43 <sup>(2)(3)(4)</sup>  | Continuous                              |      |

| Operating temperature, T <sub>A</sub> <sup>(4)</sup>                                |                            | -40 to +150                             | °C   |

| Storage temperature, T <sub>A</sub>                                                 |                            | -55 to +150                             |      |

| Junction temperature, T <sub>J</sub>                                                |                            | +150                                    |      |

|                                                                                     | Human body model (HBM)     | 3000                                    | V    |

| ESD ratings                                                                         | Machine model (MM)         | 200                                     | V    |

|                                                                                     | Charged device model (CDM) | 500                                     | V    |

<sup>(1)</sup> Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied.

(3) Short-circuit to ground.

2

<sup>(2)</sup> Input terminals are diode-clamped to the power-supply rails. Input signals that can swing more than 0.4 V beyond the supply rails should be current limited to 10 mA or less. Output terminals are diode-clamped to the power-supply rails. Output signals that can swing more than 0.4 V beyond the supply rails should be current limited to 10 mA or less.

<sup>(4)</sup> The AFE031 automatically goes into shutdown at junction temperatures that exceed +150°C.

# **ELECTRICAL CHARACTERISTICS: Transmitter (Tx)**

At  $T_J$  = +25°C, PA\_V<sub>S</sub> = 16 V,  $V_{AVDD}$  =  $V_{DVDD}$  = 3.3 V, and 10 k $\Omega$  connected to PA\_ISET (pin 46), unless otherwise noted.

|                                                      |                |                                                      |           | AFE031 |                 |        |

|------------------------------------------------------|----------------|------------------------------------------------------|-----------|--------|-----------------|--------|

| PARAMETER                                            |                | CONDITIONS                                           | MIN       | TYP    | MAX             | UNIT   |

| Tx_DAC                                               | •              |                                                      |           | •      | · ·             |        |

| Output range                                         |                |                                                      | GND + 0.1 |        | $AV_{DD} - 0.1$ | V      |

| Resolution                                           |                | 1,024 steps, 10-bit DAC                              |           | 3.2    |                 | mV     |

| Total harmonic distortion at 62.5 kHz <sup>(1)</sup> | THD            |                                                      |           |        |                 |        |

| Second harmonic distortion                           |                |                                                      |           | -73    |                 | dB     |

| Third harmonic distortion                            |                |                                                      |           | -56    |                 | dB     |

| Fourth harmonic distortion                           |                |                                                      |           | -94    |                 | dB     |

| Data rate                                            |                |                                                      |           | 1.5    |                 | MSPS   |

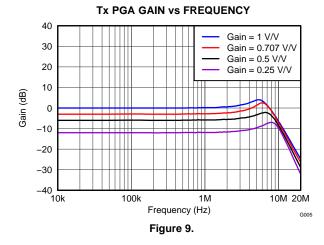

| Tx_PGA                                               |                |                                                      |           |        | 11              |        |

| Input                                                |                |                                                      |           |        |                 |        |

| Input voltage range                                  |                |                                                      | GND - 0.1 |        | $AV_{DD} + 0.1$ | V      |

|                                                      |                | G = 1 V/V                                            |           | 58     |                 | kΩ     |

|                                                      | _              | G = 0.707 V/V                                        |           | 68     |                 | kΩ     |

| Input resistance                                     | R <sub>I</sub> | G = 0.5 V/V                                          |           | 77     |                 | kΩ     |

|                                                      |                | G = 0.25 V/V                                         |           | 92     |                 | kΩ     |

| Frequency Response                                   | ·              |                                                      | ,         |        | *               |        |

|                                                      |                | DAC mode enabled                                     |           |        |                 |        |

|                                                      |                | G = 1 V/V                                            |           | 8      |                 | MHz    |

| Bandwidth                                            | BW             | G = 0.707 V/V                                        |           | 9      |                 | MHz    |

|                                                      |                | G = 0.5 V/V                                          |           | 10     |                 | MHz    |

|                                                      |                | G = 0.25 V/V                                         |           | 12     |                 | MHz    |

| Output                                               |                |                                                      |           |        |                 |        |

| Voltage output swing from AGND or AV <sub>DD</sub>   | Vo             | $R_{LOAD}$ = 10 kΩ, connected to $AV_{DD}/2$         |           | 10     | 100             | mV     |

| Maximum continuous                                   |                | Sourcing                                             |           | 25     |                 | mA     |

| current, dc                                          | Io             | Sinking                                              |           | 25     |                 | mA     |

| Output resistance                                    | Ro             | f = 100 kHz                                          |           | 1      |                 | Ω      |

| Gain                                                 | I              |                                                      |           |        | l               |        |

| Gain error                                           |                | For all gains                                        | -1        | ±0.1   | +1              | %      |

| Gain error drift                                     |                | $T_J = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ |           | 6      |                 | ppm/°C |

<sup>(1)</sup> Total harmonic distortion measured at output of Tx\_PGA configured in a gain of 1 V/V with an amplitude of 3 V<sub>PP</sub>, at a 1-MHz sample rate.

# **ELECTRICAL CHARACTERISTICS: Transmitter (Tx) (continued)**

At  $T_J$  = +25°C, PA\_V<sub>S</sub> = 16 V,  $V_{AVDD}$  =  $V_{DVDD}$  = 3.3 V, and 10 k $\Omega$  connected to PA\_ISET (pin 46), unless otherwise noted.

| PARAMETER                                                     | CONDITIONS                                            | MIN       | TYP | MAX                    | UNIT              |

|---------------------------------------------------------------|-------------------------------------------------------|-----------|-----|------------------------|-------------------|

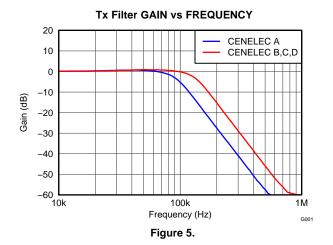

| Tx_FILTER                                                     |                                                       |           |     | *                      |                   |

| Input                                                         |                                                       |           |     |                        |                   |

| Input voltage range                                           |                                                       | GND - 0.1 |     | AV <sub>DD</sub> + 0.1 | V                 |

| Input resistance<br>(Tx_F_IN1 and Tx_F_IN2)                   |                                                       |           | 43  |                        | kΩ                |

| Frequency Response                                            |                                                       |           |     | <u> </u>               |                   |

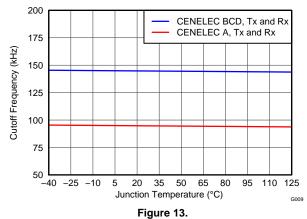

| CENELEC A Mode                                                |                                                       |           |     |                        |                   |

| Passband frequency                                            | −3 dB                                                 |           | 95  |                        | kHz               |

| Stop band attenuation                                         |                                                       | -50       | -60 |                        | dB                |

| Stop band frequency                                           |                                                       |           | 910 |                        | kHz               |

| Filter gain                                                   |                                                       |           | 0   |                        | dB                |

| CENELEC B/C/D Modes                                           |                                                       |           |     |                        |                   |

| Passband frequency                                            | −3 dB                                                 |           | 145 |                        | kHz               |

| Stop band attenuation                                         |                                                       | -50       | -60 |                        | dB                |

| Stop band frequency                                           |                                                       |           | 870 |                        | kHz               |

| Filter gain                                                   |                                                       |           | 0   |                        | dB                |

| Output                                                        |                                                       |           |     | ·                      |                   |

| Voltage output swing from $$\rm V_{O}$$ AGND or $\rm AV_{DD}$ | $R_{LOAD}$ = 10 kΩ, connected to AV <sub>DD</sub> /2  |           | 10  | 100                    | mV                |

| Maximum continuous                                            | Sourcing                                              |           | 25  |                        | mA                |

| current, dc                                                   | Sinking                                               |           | 25  |                        | mA                |

| Output resistance R <sub>O</sub>                              | f = 100 kHz                                           |           | 1   |                        | Ω                 |

| Transmitter Noise                                             |                                                       |           |     | Ÿ                      |                   |

| Integrated noise at PA output (2)                             |                                                       |           |     |                        |                   |

| CENELEC Band A<br>(40 kHz to 90 kHz)                          | Noise-reducing capacitor = 1 nF from pin 19 to ground |           | 435 |                        | μV <sub>RMS</sub> |

| CENELEC Bands B/C/D<br>(95 kHz to 140 kHz)                    | Noise-reducing capacitor = 1 nF from pin 19 to ground |           | 460 |                        | μV <sub>RMS</sub> |

<sup>(2)</sup> Includes DAC, Tx\_PGA, Tx\_Filter, PA, and REF1 bias generator.

Product Folder Link(s): AFE031

# **ELECTRICAL CHARACTERISTICS: Power Amplifier (PA)**

At  $T_J$  = +25°C, PA\_V<sub>S</sub> = 16 V,  $V_{AVDD}$  =  $V_{DVDD}$  = 3.3 V, and 10 k $\Omega$  connected to PA\_ISET (pin 46), unless otherwise noted.

|                                  |                |                                                        |                         | AFE031                        |                         |          |

|----------------------------------|----------------|--------------------------------------------------------|-------------------------|-------------------------------|-------------------------|----------|

| PARAMETER                        | CONDITIONS     |                                                        | MIN                     | TYP                           | MAX                     | UNIT     |

| Input                            |                |                                                        |                         |                               | •                       |          |

| Input voltage range              |                |                                                        | GND - 0.1               |                               | PA_V <sub>S</sub> + 0.1 | V        |

| Input resistance                 | $R_{l}$        |                                                        |                         | 20                            |                         | kΩ       |

| Frequency Response               |                |                                                        |                         |                               |                         |          |

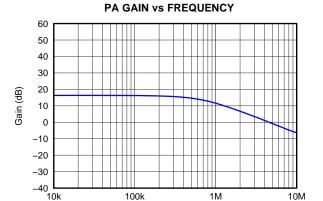

| Bandwidth E                      | 3W             | $I_{LOAD} = 0$                                         |                         | 670                           |                         | kHz      |

| Slew rate                        | SR             | 10-V step                                              |                         | 19                            |                         | V/µs     |

| Full-power bandwidth             |                | V <sub>OUT</sub> = 10 V <sub>PP</sub>                  |                         | 300                           |                         | kHz      |

| AC PSRR                          |                | f = 50 kHz                                             |                         | 14                            |                         | dB       |

| Output                           |                |                                                        |                         |                               |                         |          |

| Voltage output swing from        | .,             | I <sub>O</sub> = 300 mA, sourcing                      |                         | 0.3                           | 1                       | V        |

| PA_V <sub>S</sub>                | V <sub>O</sub> | $I_O = 1.5 A$ , sourcing                               |                         | 1.7                           | 2                       | V        |

| Voltage output swing from        | . ,            | I <sub>O</sub> = 300 mA, sinking                       |                         | 0.3                           | 1                       | V        |

| PA_Gnd                           | Vo             | I <sub>O</sub> = 1.5 A, sinking                        |                         | 1.3                           | 2                       | V        |

| Maximum continuous current, dc   | Io             | 7.5 kΩ connected to PA_I <sub>SET</sub>                | 1.5                     |                               |                         | Α        |

| Maximum peak current, ac         |                | $T_J = -40$ °C to +125°C; f = 50 kHz                   |                         | 1.7                           |                         | Α        |

| Output resistance                | Ro             | I <sub>O</sub> = 1.5 A                                 |                         | 0.1                           |                         | Ω        |

| PA disabled                      |                |                                                        |                         |                               |                         |          |

| Output impedance                 |                | f = 100 kHz, REF1 enabled                              |                         | 145 II 120                    |                         | kΩ II pF |

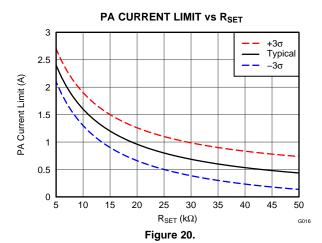

| Output current limit range       |                |                                                        |                         | ±0.4 to ±1.5                  |                         | Α        |

| Ourseast Facility and the co     |                |                                                        | I <sub>LIM</sub> = 20 k | Ω • [1.2 V/(R <sub>SE1</sub>  | <sub>Γ</sub> + 5 kΩ)]   | Α        |

| Current limit equation           |                | Solved for R <sub>SET</sub> (Current Limit)            | R <sub>SET</sub> = [(20 | 0 kΩ • 1.2 V/I <sub>LIN</sub> | <sub>1</sub> ) – 5 kΩ]  | Ω        |

| Gain                             |                | $R_{LOAD} = 1 k\Omega$                                 |                         |                               | <u> </u>                |          |

| Nominal gain                     | G              |                                                        |                         | 6.5                           |                         | V/V      |

| Gain error                       |                |                                                        | -1                      | 0.1                           | +1                      | %        |

| Gain error drift                 |                | $T_{J} = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ |                         | ±1                            |                         | ppm/°C   |

| TSENSE Diode                     | ,              |                                                        |                         | •                             |                         |          |

| Diode ideality factor            | η              |                                                        |                         | 1.033                         |                         |          |

| Thermal Shutdown                 |                |                                                        |                         |                               | ,                       |          |

| Junction temperature at shutdown |                |                                                        |                         | +160                          |                         | °C       |

| Hysteresis                       |                |                                                        |                         | 15                            |                         | °C       |

| Return to normal operation       |                |                                                        |                         | +145                          |                         | °C       |

# **ELECTRICAL CHARACTERISTICS: Receiver (Rx)**

At  $T_1 = +25$ °C,  $PA_V_S = 16 \text{ V}$ ,  $V_{AVDD} = V_{DVDD} = 3.3 \text{ V}$ , and  $10 \text{ k}\Omega$  connected to  $PA_ISET$  (pin 46), unless otherwise noted.

|                                                    |                 |                                                            |           | AFE031 |                        |          |

|----------------------------------------------------|-----------------|------------------------------------------------------------|-----------|--------|------------------------|----------|

| PARAMETER                                          |                 | CONDITIONS                                                 | MIN       | TYP    | MAX                    | UNIT     |

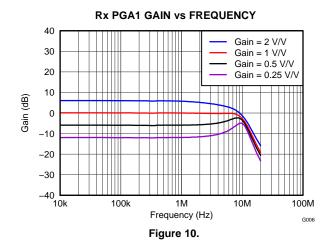

| Rx PGA1                                            |                 |                                                            |           |        |                        |          |

| Input                                              |                 |                                                            |           |        |                        |          |

| Input voltage range                                |                 |                                                            |           | 10     |                        | $V_{PP}$ |

|                                                    |                 | G = 2 V/V                                                  |           | 10     |                        | kΩ       |

|                                                    |                 | G = 1 V/V                                                  |           | 15     |                        | kΩ       |

| Input resistance                                   | R <sub>I</sub>  | G = 0.5 V/V                                                |           | 20     |                        | kΩ       |

|                                                    |                 |                                                            |           | 24     |                        | kΩ       |

| Frequency Response                                 | I               |                                                            | 1         |        | "                      |          |

|                                                    |                 | G = 2 V/V                                                  |           | 6      |                        | MHz      |

|                                                    |                 | G = 1 V/V                                                  |           | 10     |                        | MHz      |

| Bandwidth E                                        | 3W -            | G = 0.5 V/V                                                |           | 13     |                        | MHz      |

|                                                    |                 | G = 0.25 V/V                                               |           | 15     |                        | MHz      |

| Output                                             |                 |                                                            |           |        |                        |          |

| Voltage output swing from AGND or AV <sub>DD</sub> | Vo              | $R_{LOAD}$ = 6 kΩ, connected to AV <sub>DD</sub> /2        |           | 10     | 100                    | mV       |

|                                                    |                 | Sourcing                                                   |           | 25     |                        | mA       |

| Maximum continuous current, dc                     | l <sub>O</sub>  | Sinking                                                    |           | 25     |                        | mA       |

| Output resistance                                  | Ro              | G = 1, f = 100 kHz                                         |           | 1      |                        | Ω        |

| Gain                                               | -               |                                                            |           |        |                        |          |

|                                                    |                 | G = 0.25 V/V                                               | -1        | ±0.1   | +1                     | %        |

|                                                    |                 | G = 0.5 V/V                                                | -1        | ±0.1   | +1                     | %        |

| Gain error                                         |                 | G = 1 V/V                                                  | -1        | ±0.1   | +1                     | %        |

|                                                    | -               | G = 2 V/V                                                  | -2        | ±0.2   | +2                     | %        |

| Gain error drift                                   |                 | $T_J = -40^{\circ}\text{C to } +125^{\circ}\text{C}$       |           | 1      |                        | ppm/°C   |

| Rx Filter                                          |                 | · ·                                                        |           |        |                        |          |

| Input                                              |                 |                                                            |           |        |                        |          |

| Input voltage range                                |                 |                                                            | GND - 0.1 |        | AV <sub>DD</sub> + 0.1 | V        |

|                                                    | R <sub>IN</sub> |                                                            |           | 6      |                        | kΩ       |

| Frequency Response                                 |                 |                                                            |           |        |                        |          |

| CENELEC A Mode                                     |                 | Rx_C1 = 680 pF, Rx_C2 = 680 pF                             |           |        |                        |          |

| Passband frequency                                 |                 | -3 dB                                                      |           | 90     |                        | kHz      |

| Stop band attentuation                             |                 |                                                            | -25       | -33    |                        | dB       |

| Stop band frequency                                |                 |                                                            |           | 270    |                        | kHz      |

| Filter gain                                        |                 |                                                            |           | 0      |                        | dB       |

| CENELEC B/C/D Modes                                |                 | Rx_C1 = 270 pF, Rx_C2 = 560 pF                             |           |        |                        |          |

| Passband frequency                                 |                 | -3 dB                                                      |           | 145    |                        | kHz      |

| Stop band attentuation                             |                 | -                                                          | -23       | -27    |                        | dB       |

| Stop band frequency                                |                 |                                                            |           | 350    |                        | kHz      |

| Filter gain                                        |                 |                                                            |           | 0      |                        | dB       |

| Output                                             |                 |                                                            |           |        |                        |          |

| Voltage output swing from                          | Vo              | $R_{LOAD} = 10 \text{ k}\Omega$ , connected to $AV_{DD}/2$ |           | 10     | 100                    | mV       |

|                                                    |                 | Sourcing                                                   |           | 25     |                        | mA       |

| Maximum continuous current, dc                     | IO              | Sinking                                                    |           | 25     |                        | mA       |

| Output resistance                                  | Ro              | f = 100 kHz                                                |           | 5      |                        | Ω        |

Product Folder Link(s): AFE031

# **ELECTRICAL CHARACTERISTICS: Receiver (Rx) (continued)**

At  $T_J$  = +25°C, PA\_V<sub>S</sub> = 16 V,  $V_{AVDD}$  =  $V_{DVDD}$  = 3.3 V, and 10 k $\Omega$  connected to PA\_ISET (pin 46), unless otherwise noted.

|                                                    |                |                                                            |           | AFE031 |                 |               |  |

|----------------------------------------------------|----------------|------------------------------------------------------------|-----------|--------|-----------------|---------------|--|

| PARAMETER                                          |                | CONDITIONS                                                 | MIN       | TYP    | MAX             | UNIT          |  |

| Rx PGA2                                            | •              |                                                            | •         | •      | · ·             |               |  |

| Input                                              |                |                                                            |           |        |                 |               |  |

| Input voltage range                                |                |                                                            | GND - 0.1 |        | $AV_{DD} + 0.1$ | V             |  |

|                                                    |                | G = 64 V/V                                                 |           | 1.7    |                 | kΩ            |  |

| Input impedance                                    | В              | G = 16 V/V                                                 |           | 6.3    |                 | kΩ            |  |

| Input impedance                                    | R <sub>I</sub> | G = 4 V/V                                                  |           | 21     |                 | kΩ            |  |

|                                                    |                | G = 1 V/V                                                  |           | 53     |                 | kΩ            |  |

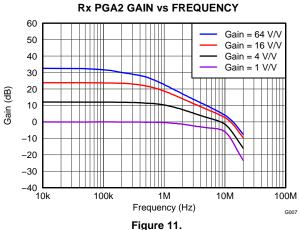

| Frequency Response                                 |                |                                                            |           |        |                 |               |  |

| equency morphism                                   |                | G = 64 V/V                                                 |           | 300    |                 | kHz           |  |

| Bandwidth                                          | BW             | G = 16 V/V                                                 |           | 800    |                 | kHz           |  |

| Dariuwiutii                                        | DVV            | G = 4 V/V                                                  |           | 1.4    |                 | MHz           |  |

|                                                    |                | G = 1 V/V                                                  |           | 4      |                 | MHz           |  |

| Output                                             |                |                                                            |           |        |                 |               |  |

| Voltage output swing from AGND or AV <sub>DD</sub> | Vo             | $R_{LOAD} = 10 \text{ k}\Omega$ , connected to $AV_{DD}/2$ |           | 10     | 100             | mV            |  |

| Maximum continuous current de                      |                | Sourcing                                                   |           | 25     |                 | mA            |  |

| Maximum continuous current, dc                     | Io             | Sinking                                                    |           | 25     |                 | mA            |  |

| Output impedance                                   | Ro             | G = 1, f = 100 kHz                                         |           | 1      |                 | Ω             |  |

| Gain                                               |                |                                                            |           |        |                 |               |  |

|                                                    |                | G = 1 V/V                                                  | -2        | ±1     | 2               | %             |  |

| Gain error                                         |                | G = 4 V/V                                                  | -2        | ±1     | 2               | %             |  |

| Gain enoi                                          |                | G = 16 V/V                                                 | -2        | ±1     | 2               | %             |  |

|                                                    |                | G = 64 V/V                                                 | -4        | ±1     | 4               | %             |  |

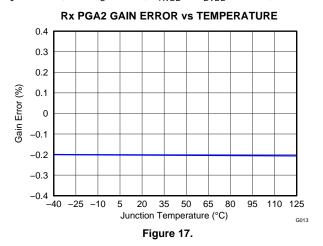

| Gain error drift                                   |                | $T_J = -40^{\circ}\text{C to } +125^{\circ}\text{C}$       |           | 6      |                 | ppm/°C        |  |

| Rx Sensitivity                                     |                |                                                            |           |        |                 |               |  |

| Integrated noise, RTI <sup>(1)</sup>               |                |                                                            |           |        |                 |               |  |

| CENELEC Band A<br>(40 kHz to 90 kHz)               |                | Noise-reducing capacitor = 1 µF from pin 28 to ground      |           | 14     |                 | $\mu V_{RMS}$ |  |

| CENELEC Bands B/C/D<br>(95 kHz to 140 kHz)         |                | Noise-reducing capacitor = 1 μF from pin 28 to ground      |           | 11     |                 | $\mu V_{RMS}$ |  |

<sup>(1)</sup> Includes Rx PGA1, Rx\_Filter, Rx PGA2, and REF2 bias generator.

# **ELECTRICAL CHARACTERISTICS: Digital**

At  $T_J$  = +25°C, PA\_V<sub>S</sub> = 16 V,  $V_{AVDD}$  =  $V_{DVDD}$  = 3.3 V, and 10 k $\Omega$  connected to PA\_ISET (pin 46), unless otherwise noted.

|                                                     |                 |                              |                        | AFE031                    |                        |      |

|-----------------------------------------------------|-----------------|------------------------------|------------------------|---------------------------|------------------------|------|

| PARAMETER                                           |                 | CONDITIONS                   | MIN                    | TYP                       | MAX                    | UNIT |

| Digital Inputs (SCLK, DIN, $\overline{\text{CS}}$ , | DAC, SE         | 0)                           |                        |                           |                        |      |

| Leakage input current                               |                 | $0 \le V_{IN} \le DV_{DD}$   | -1                     | 0.01                      | 1                      | μΑ   |

| Input logic levels                                  |                 |                              |                        |                           |                        |      |

| High-level input voltage                            | V <sub>IH</sub> |                              | 0.7 • DV <sub>DD</sub> |                           |                        | V    |

| Low-level input voltage                             | $V_{IL}$        |                              |                        |                           | 0.3 • DV <sub>DD</sub> | V    |

| SD pin high                                         |                 | SD > 0.7 • DV <sub>DD</sub>  | AFE                    | E031 in shutdo            | wn                     |      |

| SD pin low                                          |                 | SD < 0.3 • DV <sub>DD</sub>  | AFE03                  | 1 in normal op            | eration                |      |

| DAC pin high                                        |                 | DAC > 0.7 • DV <sub>DD</sub> | SPI acc                | cess to DAC R             | egister                |      |

| DAC pin low                                         |                 | DAC < 0.3 • DV <sub>DD</sub> | SPI acces              | s to Command<br>Registers | and Data               |      |

| Digital Outputs (DO, ZC_OUT)                        |                 |                              |                        |                           |                        |      |

| High-level output voltage                           | V <sub>O</sub>  | I <sub>OH</sub> = 3 mA       | DV <sub>DD</sub> - 0.4 |                           | DV <sub>DD</sub>       | V    |

| Low-level output voltage                            | V <sub>OL</sub> | $I_{OL} = -3 \text{ mA}$     | GND                    |                           | GND + 0.4              | V    |

| Digital Outputs (INT, Tx_Flag,                      | Rx_Flag         | )                            | 1                      |                           |                        |      |

| High-level output current                           | I <sub>OH</sub> | V <sub>OH</sub> = 3.3 V      |                        |                           | 1                      | μΑ   |

| Low-level output voltage                            | V <sub>OL</sub> | I <sub>OL</sub> = 4 mA       |                        |                           | 0.4                    | V    |

| Low-level output current                            | I <sub>OL</sub> | V <sub>OL</sub> = 400 mV     | 4                      |                           |                        | mA   |

| INT pin high (open drain)                           |                 | INT sink current < 1 μA      | N                      | ormal operatio            | n                      |      |

| INT pin low (open drain) <sup>(1)</sup>             |                 | INT < 0.4 V                  | Indicates a            | an interrupt has          | s occurred             |      |

| Tx_Flag high (open drain)                           |                 | Tx_Flag sink current < 1 μA  | Indicat                | tes Tx block is           | ready                  |      |

| Tx_Flag low (open drain)                            |                 | Tx_Flag < 0.4 V              | Indicates              | s Tx block is no          | ot ready               |      |

| Rx_Flag high (open drain)                           |                 | Rx_Flag sink current < 1 μA  | Indicat                | tes Rx block is           | ready                  |      |

| Rx_Flag low (open drain)                            |                 | Rx_Flag < 0.4 V              | Indicates              | s Rx block is n           | ot ready               |      |

| DIGITAL TIMING                                      |                 |                              |                        |                           |                        |      |

| Gain Timing                                         |                 |                              |                        |                           |                        |      |

| Gain select time                                    |                 |                              |                        | 0.2                       |                        | μs   |

| Shutdown Mode Timing                                |                 |                              |                        |                           | -                      |      |

| Enable time                                         |                 |                              |                        | 4.0                       |                        | μs   |

| Disable time                                        |                 |                              |                        | 2.0                       |                        | μs   |

| POR Timing                                          |                 |                              | <u> </u>               |                           | 1                      |      |

| Power-On Reset power-up                             | time            | DV <sub>DD</sub> ≥ 2 V       |                        | 50                        |                        | μs   |

<sup>(1)</sup> When an interrupt is detected (INT pin low), the contents of the I\_Flag and T\_Flag Registers can be read to determine the reason for the interrupt.

Product Folder Link(s): AFE031

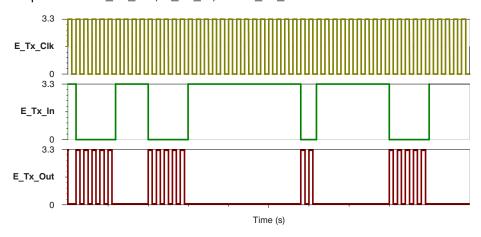

### **ELECTRICAL CHARACTERISTICS: Two-Wire Interface**

At  $T_J = +25$ °C,  $PA_V_S = 16$  V,  $V_{AVDD} = V_{DVDD} = 3.3$  V, and 10 k $\Omega$  connected to  $PA_ISET$  (pin 46), unless otherwise noted.

|                                           |                 |                                    |                        | AFE031 |                        |      |

|-------------------------------------------|-----------------|------------------------------------|------------------------|--------|------------------------|------|

| PARAMETER                                 |                 | CONDITIONS                         | MIN                    | TYP    | MAX                    | UNIT |

| TWO-WIRE TRANSMITTER                      |                 |                                    |                        |        | •                      |      |

| Frequency range <sup>(1)</sup>            |                 |                                    |                        | 50     |                        | kHz  |

| Leakage input current (E_Tx_In, E_Tx_Clk) |                 | $0 \le V_{IN} \le DV_{DD}$         | -1                     | 0.01   | 1                      | μΑ   |

| Input logic levels (E_Tx_In, E_Tx_Clk     | <b>(</b> )      |                                    |                        |        |                        |      |

| High-level input voltage                  | $V_{IH}$        |                                    | 0.7 • DV <sub>DD</sub> |        |                        | V    |

| Low-level input voltage                   | $V_{IL}$        |                                    |                        |        | 0.3 • DV <sub>DD</sub> | V    |

| Output logic levels (E_Tx_Out)            |                 |                                    |                        |        |                        |      |

| High-level output voltage                 | V <sub>O</sub>  | $I_{OH} = 3 \text{ mA}$            | AV <sub>DD</sub> – 0.4 |        | AV <sub>DD</sub>       | V    |

| Low-level output voltage                  | V <sub>OL</sub> | $I_{OL} = -3 \text{ mA}$           | GND                    |        | GND + 0.4              | V    |

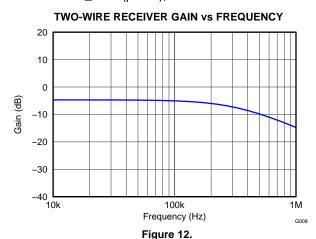

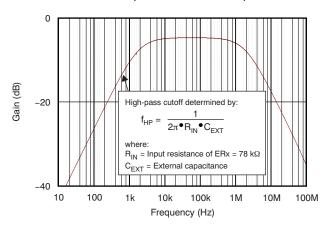

| TWO-WIRE RECEIVER                         |                 |                                    |                        |        |                        |      |

| Gain                                      |                 |                                    |                        | -4.5   |                        | dB   |

| Frequency range                           |                 |                                    |                        | 300    |                        | kHz  |

| Max sink current                          |                 |                                    |                        | 25     |                        | mA   |

| Max source current                        |                 |                                    |                        | 25     |                        | mA   |

| Input terminal offset                     |                 | Referenced to V <sub>AVDD</sub> /2 | -100                   | 10     | 100                    | mV   |

| Input impedance                           |                 |                                    |                        | 78     |                        | kΩ   |

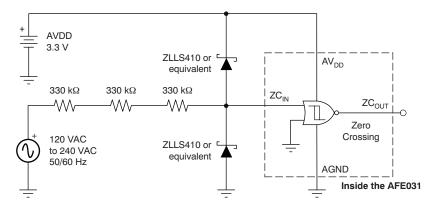

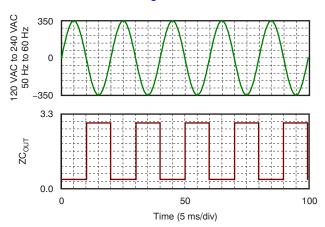

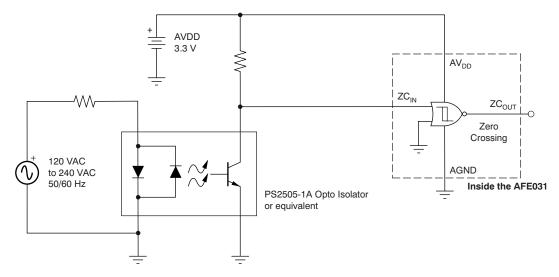

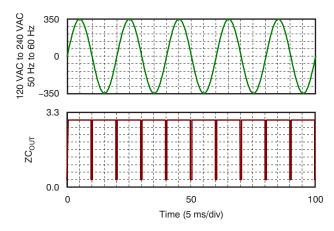

| ZERO CROSSING DETECTOR                    |                 |                                    |                        |        |                        |      |

| Input voltage range                       |                 |                                    | AV <sub>DD</sub> – 0.4 |        | $AV_{DD} + 0.4$        | V    |

| Input current range                       |                 |                                    | -10                    |        | +10                    | mA   |

| Input capacitance                         |                 |                                    |                        | 3      |                        | pF   |

| Rising threshold                          |                 |                                    | 0.45                   | 0.9    | 1.35                   | V    |

| Falling threshold                         |                 |                                    | 0.25                   | 0.5    | 0.75                   | V    |

| Hysteresis                                |                 |                                    | 0.20                   | 0.4    | 0.60                   | V    |

| Jitter                                    |                 | 50 Hz, 240 V <sub>RMS</sub>        |                        | 10     |                        | ns   |

<sup>(1)</sup> The two-wire transmitter circuit is tested at  $Tx_CLK = 10 MHz$ .

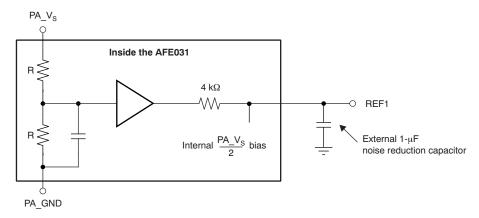

### **ELECTRICAL CHARACTERISTICS: Internal Bias Generator**

At  $T_J = +25$ °C,  $PA_V_S = 16$  V,  $V_{AVDD} = V_{DVDD} = 3.3$  V, and 10 k $\Omega$  connected to  $PA_ISET$  (pin 46), unless otherwise noted.

|                  |                                                       |     | AFE031               |     |      |

|------------------|-------------------------------------------------------|-----|----------------------|-----|------|

| PARAMETER        | CONDITIONS                                            | MIN | TYP                  | MAX | UNIT |

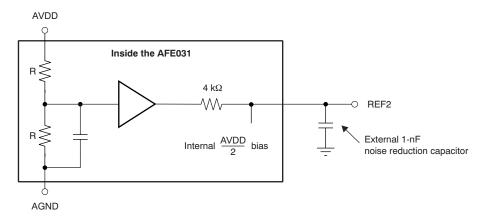

| REF1 (Pin 19)    |                                                       |     |                      |     |      |

| Bias voltage     |                                                       |     | PA_V <sub>S</sub> /2 |     | V    |

| Input resistance | 1                                                     |     | 4                    |     | kΩ   |

| Turn-on time     | Noise-reducing capacitor = 1 nF from pin 19 to ground |     | 20                   |     | ms   |

| Turn-off time    | Noise-reducing capacitor = 1 nF from pin 19 to ground |     | 20                   |     | ms   |

| REF2 (Pin 28)    |                                                       |     |                      |     |      |

| Bias voltage     |                                                       |     | V <sub>AVDD</sub> /2 |     | V    |

| Input resistance | 1                                                     |     | 4                    |     | kΩ   |

| Turn-on time     | Noise-reducing capacitor = 1 µF from pin 28 to ground |     | 20                   |     | ms   |

| Turn-off time    | Noise-reducing capacitor = 1 µF from pin 28 to ground |     | 20                   |     | ms   |

## **ELECTRICAL CHARACTERISTICS: Power Supply**

At  $T_J$  = +25°C, PA\_V<sub>S</sub> = 16 V,  $V_{AVDD}$  =  $V_{DVDD}$  = 3.3 V, and 10 k $\Omega$  connected to PA\_ISET (pin 46), unless otherwise noted.

|                                |                     |                                             |      | AFE031   |      |      |  |

|--------------------------------|---------------------|---------------------------------------------|------|----------|------|------|--|

| PARAMETER                      |                     | CONDITIONS                                  | MIN  | TYP      | MAX  | UNIT |  |

| Operating Supply Range         |                     |                                             | •    |          |      |      |  |

| Power amplifier supply voltage | PA_V <sub>S</sub>   |                                             | +7   |          | +24  | V    |  |

| Digital supply voltage         | DV <sub>DD</sub>    |                                             | +3.0 |          | +3.6 | V    |  |

| Analog supply voltage          | AV <sub>DD</sub>    |                                             | +3.0 |          | +3.6 | V    |  |

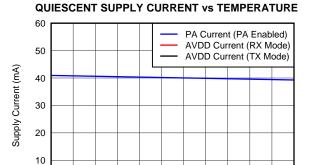

| Quiescent Current              |                     | SD pin low                                  |      |          | ·    |      |  |

| Danier and life and annual t   |                     | I <sub>O</sub> = 0, PA = On <sup>(1)</sup>  |      | 49       | 61   | mA   |  |

| Power amplifier current        | I <sub>QPA_VS</sub> | I <sub>O</sub> = 0, PA = Off <sup>(2)</sup> |      | 10       |      | μA   |  |

|                                |                     | Tx configuration (3)                        |      | 1.2      |      | mA   |  |

| Digital supply current         | I <sub>QDVDD</sub>  | Rx configuration <sup>(4)</sup>             |      | 5        |      | μA   |  |

|                                |                     | All blocks disabled <sup>(5)</sup>          |      | 5        |      | μA   |  |

|                                |                     | Tx configuration (3)                        |      | 2.8      | 3.7  | mA   |  |

| Analog supply current          | I <sub>QAVDD</sub>  | Rx configuration <sup>(4)</sup>             |      | 3.6      | 5.3  | mA   |  |

|                                |                     | All blocks disabled <sup>(5)</sup>          |      | 30       |      | μA   |  |

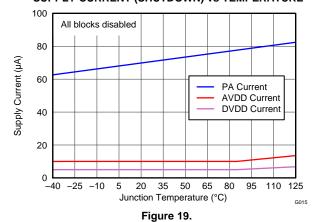

| Shutdown (SD)                  | <del>'</del>        |                                             |      |          | "    |      |  |

| Power amplifier supply voltage | PA_V <sub>S</sub>   | SD pin high                                 |      | 75       | 150  | μA   |  |

| Digital supply voltage         | $DV_DD$             | SD pin high                                 |      | 5        | 10   | μA   |  |

| Analog supply voltage          | $AV_{DD}$           | SD pin high                                 |      | 15       | 40   | μA   |  |

| Temperature                    |                     |                                             | 1    | <u> </u> |      |      |  |

| Specified range                |                     |                                             | -40  |          | +125 | °C   |  |

- (1) Enable1 Register = 00100011, Enable2 Register = 00001110.

- (2) Enable1 Register = 00000100, Enable2 Register = 00000110.

- (3) In the Tx configuration, the following blocks are enabled: DAC, Tx, PA, REF1, and REF2. All other blocks are disabled. Enable1 Register = 00100011, Enable2 Register = 00001110.

- (4) In the Rx configuration, the following blocks are enabled: Rx, REF1, and REF2. All other blocks are disabled. Enable1 Register = 00000100, Enable2 Register = 00000110.

- (5) Enable1 Register = 00000000, Enable2 Register = 00000000.

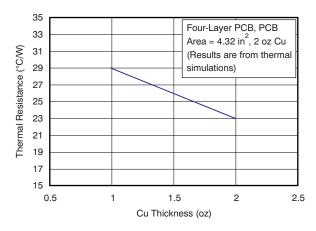

### THERMAL INFORMATION

|                         |                                              | AFE031    |       |

|-------------------------|----------------------------------------------|-----------|-------|

|                         | THERMAL METRIC <sup>(1)</sup>                | RGZ (QFN) | UNITS |

|                         |                                              | 48 PINS   |       |

| $\theta_{JA}$           | Junction-to-ambient thermal resistance       | 27.8      |       |

| $\theta_{JCtop}$        | Junction-to-case (top) thermal resistance    | 12.1      |       |

| $\theta_{JB}$           | Junction-to-board thermal resistance         | 7.5       | °C/W  |

| $\Psi_{JT}$             | Junction-to-top characterization parameter   | 0.4       | *C/VV |

| ΨЈВ                     | Junction-to-board characterization parameter | 7.4       |       |

| $\theta_{\text{JCbot}}$ | Junction-to-case (bottom) thermal resistance | 1.7       |       |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

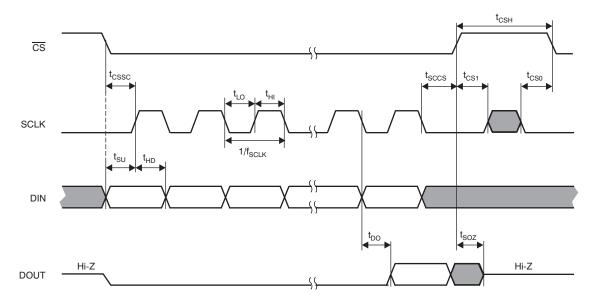

# **SPI TIMING REQUIREMENTS**

| PARAMETER                             |                   | CONDITION     | MIN | TYP | MAX | UNIT |

|---------------------------------------|-------------------|---------------|-----|-----|-----|------|

| Input capacitance                     |                   |               |     | 1   |     | рF   |

| Input rise/fall time                  | t <sub>RFI</sub>  | CS, DIN, SCLK |     |     | 2   | ns   |

| Output rise/fall time                 | t <sub>RFO</sub>  | DOUT          |     |     | 10  | ns   |

| CS high time                          | t <sub>CSH</sub>  | <del>CS</del> | 20  |     |     | ns   |

| SCLK edge to CS fall setup time       | t <sub>CS0</sub>  |               | 10  |     |     | ns   |

| CS fall to first SCLK edge setup time | tcssc             |               | 10  |     |     | ns   |

| SCLK frequency                        | f <sub>SCLK</sub> |               |     |     | 20  | MHz  |

| SCLK high time                        | t <sub>HI</sub>   |               | 20  |     |     | ns   |

| SCLK low time                         | t <sub>LO</sub>   |               | 20  |     |     | ns   |

| SCLK last edge to CS rise setup time  | t <sub>SCCS</sub> |               | 10  |     |     | ns   |

| CS rise to SCLK edge setup time       | t <sub>CS1</sub>  |               | 10  |     |     | ns   |

| DIN setup time                        | t <sub>SU</sub>   |               | 10  |     |     | ns   |

| DIN hold time                         | t <sub>HD</sub>   |               | 5   |     |     | ns   |

| SCLK to DOUT valid propagation delay  | t <sub>DO</sub>   |               |     |     | 20  | ns   |

| CS rise to DOUT forced to Hi-Z        | t <sub>soz</sub>  |               |     |     | 20  | ns   |

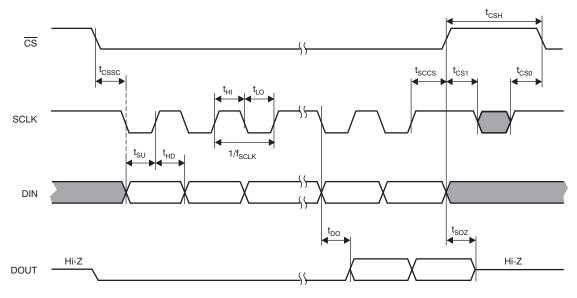

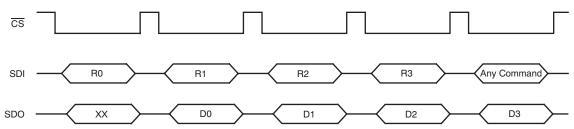

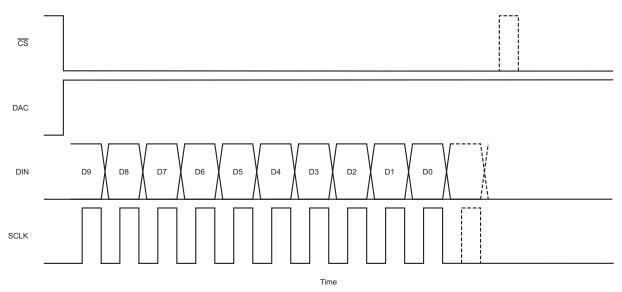

# **TIMING DIAGRAMS**

Figure 1. SPI Mode 0,0

Figure 2. SPI Mode 1,1

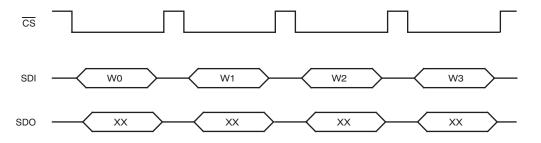

W - Command of Write Register N

XX - Don't care; undefined.

Figure 3. Write Operation in Stand-Alone Mode

R - Command of Read Register N Read

D - Data from Register N

XX - Don't care; undefined.

Figure 4. Read Operation in Stand-Alone Mode

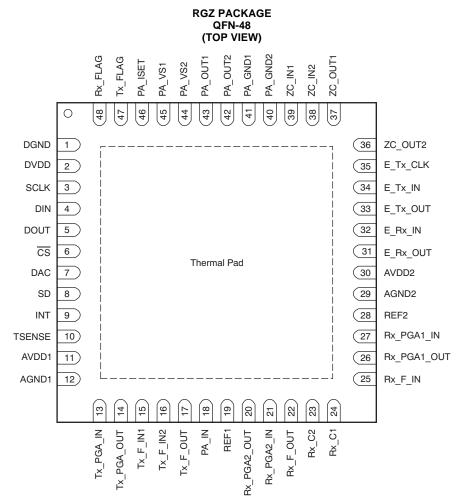

### **DEVICE INFORMATION**

### **PIN ASSIGNMENTS**

NOTE: Exposed thermal pad is connected to ground.

# **PIN DESCRIPTIONS**

| AF      | PIN DESCRIPTIONS  AFE031 |                                                           |  |  |  |  |  |

|---------|--------------------------|-----------------------------------------------------------|--|--|--|--|--|

| PIN NO. | NAME                     | DESCRIPTION                                               |  |  |  |  |  |

| 1       | DGND                     | Digital ground                                            |  |  |  |  |  |

| 2       | DVDD                     | Digital supply                                            |  |  |  |  |  |

| 3       | SCLK                     | SPI serial clock                                          |  |  |  |  |  |

| 4       | DIN                      |                                                           |  |  |  |  |  |

|         |                          | SPI digital input                                         |  |  |  |  |  |

| 5       | DOUT                     | SPI digital output                                        |  |  |  |  |  |

| 6       | CS                       | Pl digital chip select                                    |  |  |  |  |  |

| 7       | DAC                      | DAC mode select                                           |  |  |  |  |  |

| 8       | SD                       | System shutdown                                           |  |  |  |  |  |

| 9       | INT                      | Interrupt on overcurrent or thermal limit                 |  |  |  |  |  |

| 10      | TSENSE                   | Temp sensing diode (anode)                                |  |  |  |  |  |

| 11      | AVDD1                    | Analog lupply                                             |  |  |  |  |  |

| 12      | AGND1                    | Analog ground                                             |  |  |  |  |  |

| 13      | Tx_PGA_IN                | Transmit PGA Input                                        |  |  |  |  |  |

| 14      | Tx_PGA_OUT               | Transmit PGA lutput                                       |  |  |  |  |  |

| 15      | Tx_F_IN1                 | Transmit filter input 1                                   |  |  |  |  |  |

| 16      | Tx_F_IN2                 | Transmit filter input 2                                   |  |  |  |  |  |

| 17      | Tx_F_OUT                 | Transmit filter output                                    |  |  |  |  |  |

| 18      | PA_IN                    | Power Amplifier input                                     |  |  |  |  |  |

| 19      | REF1                     | Power Amplifier noise reducing capacitor                  |  |  |  |  |  |

| 20      | Rx PGA2_OUT              | Receiver PGA(2) output                                    |  |  |  |  |  |

| 21      | Rx PGA2_IN               | Receiver PGA(2) input                                     |  |  |  |  |  |

| 22      | Rx_F_OUT                 | Receiver FGA(2) input  Receiver filter output             |  |  |  |  |  |

| 23      | Rx_C2                    | Receiver external frequency select                        |  |  |  |  |  |

|         |                          |                                                           |  |  |  |  |  |

| 24      | Rx_C1                    | Receiver external frequency select                        |  |  |  |  |  |

| 25      | Rx_F_IN                  | Receiver filter input                                     |  |  |  |  |  |

| 26      | Rx PGA1_OUT              | Receiver PGA(1) output                                    |  |  |  |  |  |

| 27      | Rx PGA1_IN               | Receiver PGA(1) input                                     |  |  |  |  |  |

| 28      | REF2                     | Receiver noise reducing capacitor                         |  |  |  |  |  |

| 29      | AGND2                    | Analog ground                                             |  |  |  |  |  |

| 30      | AVDD2                    | Analog supply                                             |  |  |  |  |  |

| 31      | E_Rx_OUT                 | Two-wire receiver output                                  |  |  |  |  |  |

| 32      | E_Rx_IN                  | Two-wire receiver input                                   |  |  |  |  |  |

| 33      | E_Tx_OUT                 | Two-wire transmitter output                               |  |  |  |  |  |

| 34      | E_Tx_IN                  | Two-wire transmitter input                                |  |  |  |  |  |

| 35      | E_Tx_CLK                 | Two-wire transmitter clock input                          |  |  |  |  |  |

| 36      | ZC_OUT2                  | Zero crossing detector output                             |  |  |  |  |  |

| 37      | ZC_OUT1                  | Zero crossing detector output                             |  |  |  |  |  |

| 38      | ZC_IN2                   | Zero crossing detector input                              |  |  |  |  |  |

| 39      | ZC_IN1                   | Zero crossing detector input                              |  |  |  |  |  |

| 40      | PA_GND2                  | Power Amplifier ground                                    |  |  |  |  |  |

| 41      | PA_GND1                  | Power Amplifier ground                                    |  |  |  |  |  |

| 42      | PA_OUT2                  | Power Amplifier output                                    |  |  |  |  |  |

| 43      | PA_OUT1                  | Power Amplifier output                                    |  |  |  |  |  |

| 44      | PA_US2                   |                                                           |  |  |  |  |  |

| 45      |                          | Power Amplifier supply                                    |  |  |  |  |  |

|         | PA_VS1                   | Power Amplifier supply  Rever Amplifier support limit set |  |  |  |  |  |

| 46      | PA_ISET                  | Power Amplifier current limit set                         |  |  |  |  |  |

| 47      | Tx_FLAG                  | Transmitter ready flag                                    |  |  |  |  |  |

| 48      | Rx_FLAG                  | Receiver ready flag                                       |  |  |  |  |  |

Product Folder Link(s): AFE031

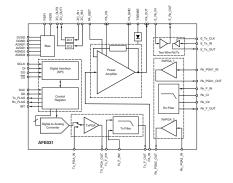

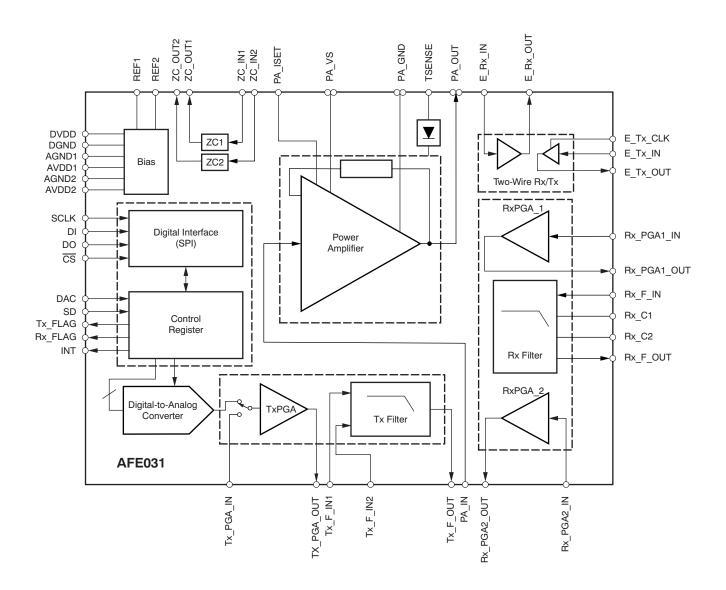

### **FUNCTIONAL BLOCK DIAGRAM**

### **TYPICAL CHARACTERISTICS**

At  $T_J = +25$ °C,  $PA_V_S = 16$  V,  $V_{AVDD} = V_{DVDD} = 3.3$  V, and 10 k $\Omega$  connected to  $PA_ISET$  (pin 46), unless otherwise noted.

100k

5

0

1k

**MAXIMUM PA OUTPUT VOLTAGE vs FREQUENCY**

Frequency (Hz) Figure 7.

1M

10M

100k

Frequency (Hz)

1M

10M

G004

10k

16

# **TYPICAL CHARACTERISTICS (continued)**

At  $T_J = +25$ °C,  $PA_V_S = 16$  V,  $V_{AVDD} = V_{DVDD} = 3.3$  V, and 10 k $\Omega$  connected to  $PA_ISET$  (pin 46), unless otherwise noted.

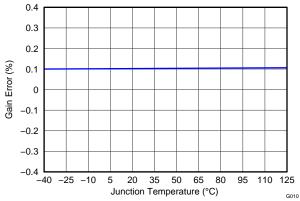

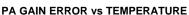

# Tx PGA GAIN ERROR vs TEMPERATURE

Figure 14.

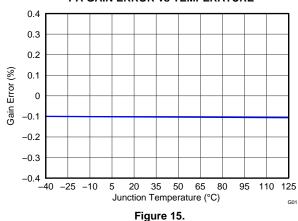

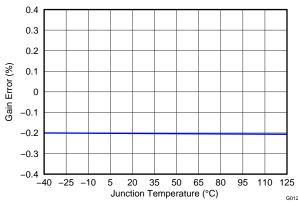

Figure 16.

95 110

125

# **TYPICAL CHARACTERISTICS (continued)**

At  $T_J = +25$ °C,  $PA_V_S = 16$  V,  $V_{AVDD} = V_{DVDD} = 3.3$  V, and 10 k $\Omega$  connected to  $PA_ISET$  (pin 46), unless otherwise noted.

Figure 18.

Junction Temperature (°C)

-40 -25 -10

5 20 35 50 65 80

### SUPPLY CURRENT (SHUTDOWN) vs TEMPERATURE

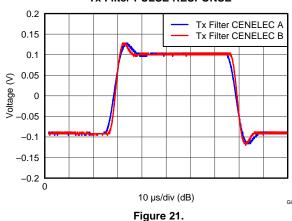

Tx Filter PULSE RESPONSE

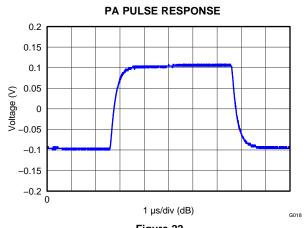

Figure 22.

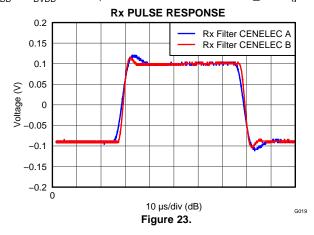

# **TYPICAL CHARACTERISTICS (continued)**

At  $T_J$  = +25°C, PA\_V<sub>S</sub> = 16 V,  $V_{AVDD}$  =  $V_{DVDD}$  = 3.3 V, and 10 k $\Omega$  connected to PA\_ISET (pin 46), unless otherwise noted.

### APPLICATION INFORMATION

### **GENERAL DESCRIPTION**

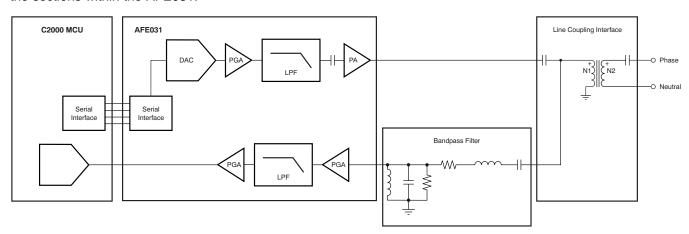

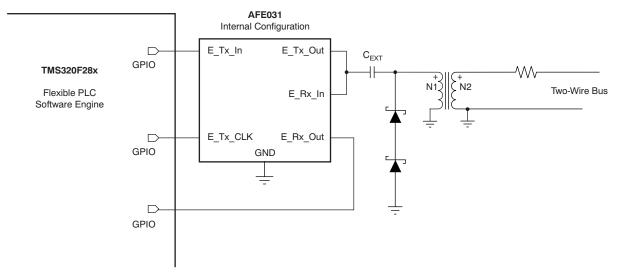

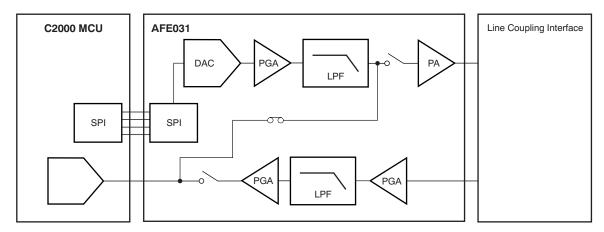

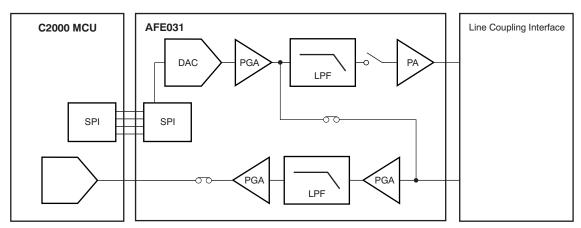

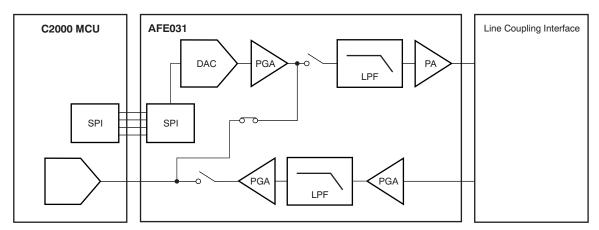

The AFE031 is an integrated powerline communication analog front-end (AFE) device built from a variety of functional blocks that work in conjunction with a microcontroller. The AFE031 provides the interface between the microcontroller and a line coupling circuit. The AFE031 delivers high performance and is designed to work with a minimum number of external components. Consisting of a variety of functional and configurable blocks, the AFE031 simplifies design efforts and reduces the time to market of many applications.

The AFE031 includes three primary functional blocks:

- Power Amplifier (PA)

- Transmitter (Tx)

- Receiver (Rx)

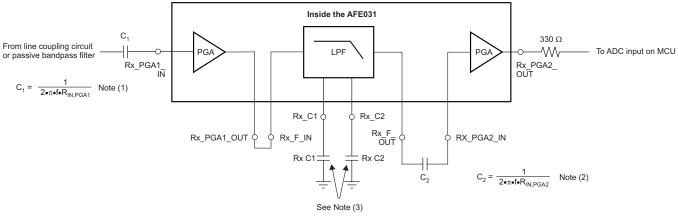

The AFE031 also consists of other support circuitry blocks that provide zero crossing detection, an additional two-wire communications channel, and power-saving biasing blocks (see the Functional Block Diagram). All of these functional blocks are digitally controlled by the microcontroller through the serial interface (SPI).

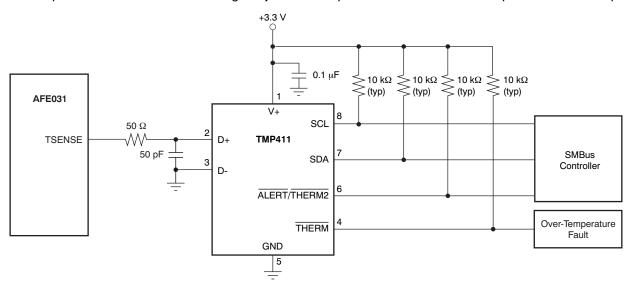

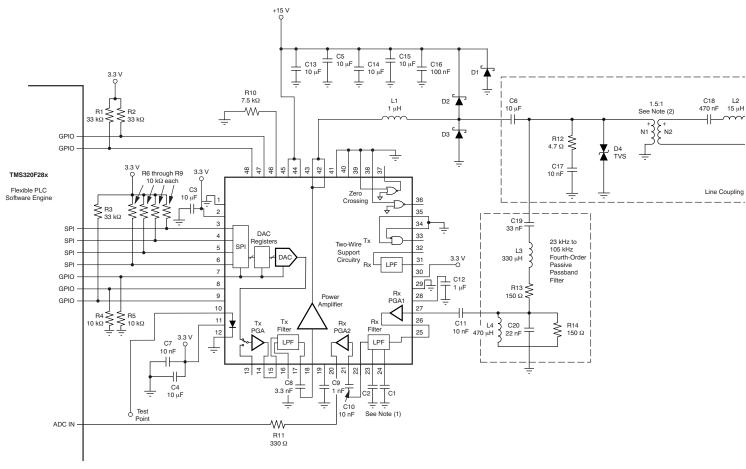

Figure 24 shows a typical powerline communications application system diagram. Table 1 is a complete list of the sections within the AFE031.

Figure 24. Typical Powerline Communications System Diagram

**Table 1. Block Descriptions**

| BLOCK | DESCRIPTION                                                                              |

|-------|------------------------------------------------------------------------------------------|

| PA    | The PA block includes the power amplifier and associated pedestal biasing circuitry      |

| Tx    | The Tx block includes the Tx_Filter and the Tx_PGA                                       |

| Rx    | The Rx block includes the Rx PGA1, the Rx Filter, and the Rx PGA2                        |

| ERx   | The ER block includes the two-wire receiver                                              |

| ETx   | The ER block includes the two-wire transmitter                                           |

| DAC   | The DAC block includes a digital-to-analog converter                                     |

| ZC    | The ZC block includes both zero crossing detectors                                       |

| REF1  | The REF1 block includes the internal bias generator for the PA block                     |

| REF2  | The REF2 block includes the internal bias generators for the Tx, Rx, ERx, and ETx blocks |

20

### **BLOCK DESCRIPTIONS**

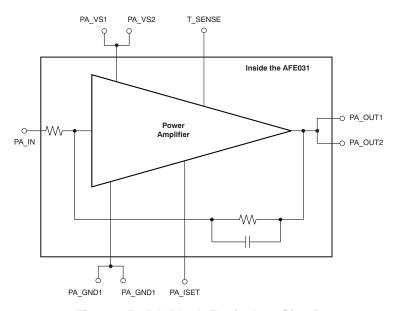

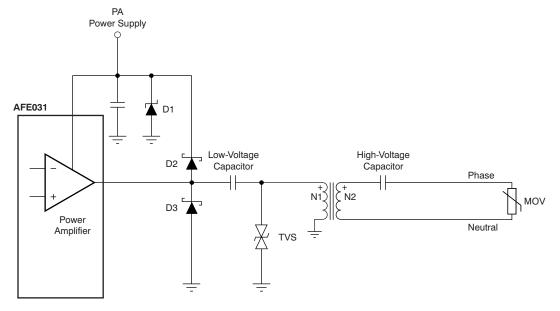

#### **PA Block**

The Power Amplifier (PA) block consists of a high slew rate, high-voltage, and high-current operational amplifier. The PA is configured with an inverting gain of 6.5 V/V, has a low-pass filter response, and maintains excellent linearity and low distortion. The PA is specified to operate from 7 V to 24 V and can deliver up to ±1.5 A of continuous output current over the specified junction temperature range of –40°C to +125°C. Figure 25 illustrates the PA block.

Figure 25. PA Block Equivalent Circuit

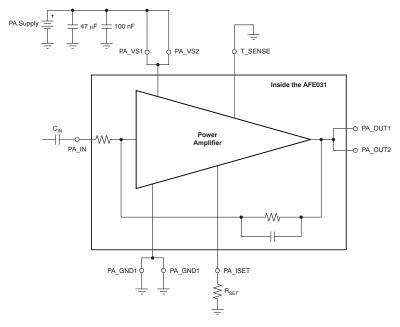

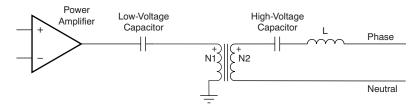

Connecting the PA in a typical PLC application requires only two additional components: an ac coupling capacitor,  $C_{IN}$ , and the current limit programming resistor,  $R_{SET}$ . Figure 26 shows the typical connections to the PA block.

Figure 26. Typical Connections to the PA

The external capacitor,  $C_{IN}$ , introduces a single-pole, high-pass characteristic to the PA transfer function; combined with the inherent low-pass transfer function, this characteristic results in a passband response. The value of the high-pass cutoff frequency is determined by  $C_{IN}$  reacting with the input resistance of the PA circuit, and can be found from Equation 1:

$$C_{IN} = \frac{1}{(2 \cdot \pi \cdot 20 \text{ k}\Omega \cdot f_{HP})}$$

(1)

#### Where:

- C<sub>IN</sub> = external input capacitor

- f<sub>HP</sub> = desired high-pass cutoff frequency

For example, setting  $C_{IN}$  to 3.3 nF results in a high-pass cutoff frequency of 2.4 kHz. The voltage rating for  $C_{IN}$  should be determined to withstand operation up to the PA power-supply voltage.

When the transmitter is not in use, the output can be disabled and placed into a high-impedance state by writing a '0' to the PA-OUT bit in the Enable2 Register. Additional power savings can be realized by shutting down the PA when not in use. Shutting down the PA for power savings is accomplished by writing a '0' to the PA bit in the Enable1 Register. Shutting down the PA also results in the PA output entering a high-impedance state. When the PA shuts down, it consumes only 2 mW of power.

The PA\_ISET pin (pin 46) provides a resistor-programmable output current limit for the PA block. Equation 2 determines the value of the external  $R_{\text{SET}}$  resistor attached to this pin.

$$R_{SET} = \left(20 \text{ k}\Omega \bullet \frac{1.2 \text{ V}}{I_{LIM}}\right) - 5 \text{ k}\Omega$$

(2)

### Where:

- R<sub>SET</sub> = the value of the external resistor connected between pin 46 and ground.

- I<sub>LIM</sub> = the value of the desired current limit for the PA.

Note that to ensure proper design margin with respect to manufacturing and temperature variations, a 30% decrease of the value used in Equation 2 for  $I_{LIM}$  over the nominal value of  $I_{LIM}$  is recommended. See Figure 20, PA Current Limit vs  $R_{SET}$ .

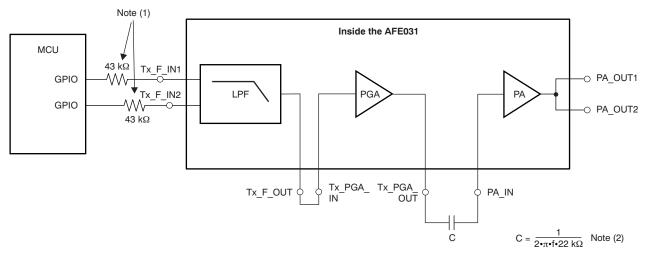

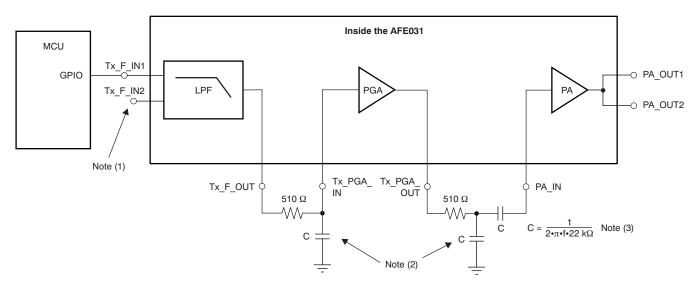

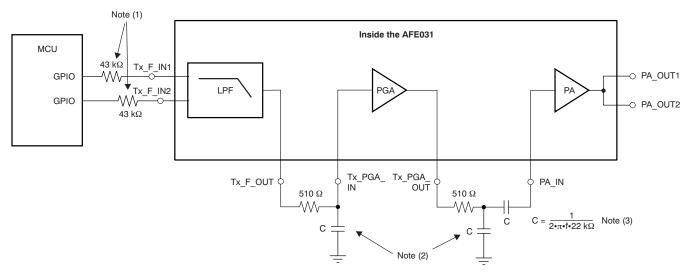

### Tx Block

The Tx block consists of the Tx PGA and Tx Filter. The Tx PGA is a low-noise, high-performance, programmable gain amplifier. In DAC mode (where pin 7 is a logical '1' and Enable1 Register bit location 5 is a logical '1'), the Tx PGA operates as the internal digital-to-analog converter (DAC) output buffer with programmable gain. In PWM mode (where pin 7 is a logical '0' and Enable1 Register bit location 5 is a logical '0'), the Tx PGA operates as a stand-alone programmable gain amplifier. The Tx PGA gain is programmed through the serial interface. The Tx PGA gain settings are 0.25 V/V, 0.5 V/V, 0.707 V/V, and 1 V/V.

The Tx Filter is a unity-gain, fourth-order low-pass filter. The Tx Filter cutoff frequency is selectable between CENELEC A or CENELEC B, C, and D modes. The Control1 Register bit location 3 setting (CA CBCD) determines the cutoff frequency. Setting Control1 Register bit location 3 to '0' selects the CENELEC A band; setting Control1 Register bit location 3 to '1' selects CENELEC B, C, and D bands.

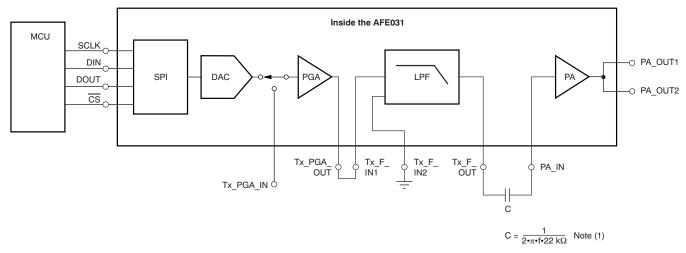

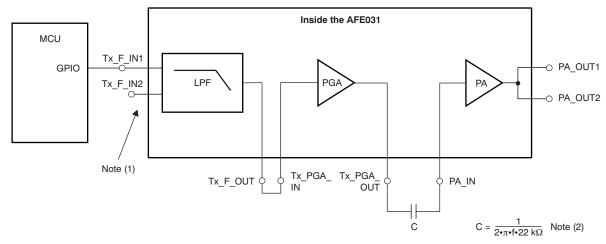

The AFE031 supports both DAC inputs or PWM inputs for the Tx signal path. DAC mode is recommended for best performance. In DAC mode, no external components in the Tx signal path are required to meet regulatory signal emissions requirements. When in DAC mode, the AFE031 accepts serial data from the microprocessor and writes that data to the internal DAC registers. When in DAC mode (where pin 7 is a logical '1' and Enable1 Register bit location 5 is a logical '1'), the Tx PGA output must be directly coupled to the Tx\_FIN1 input and the unused Tx\_FIN2 input must be grounded.

The proper connections for the Tx signal path for DAC mode operation are shown in Figure 27. Operating in DAC mode results in the lowest distortion signal injected onto the ac mains. No additional external filtering components are required to meet CENELEC requirements for A, B, C or D bands when operating in DAC mode.

(1) For capacitor value C, f is the desired lower cutoff frequency and 22 k $\Omega$  is the PA input resistance.

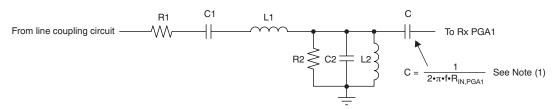

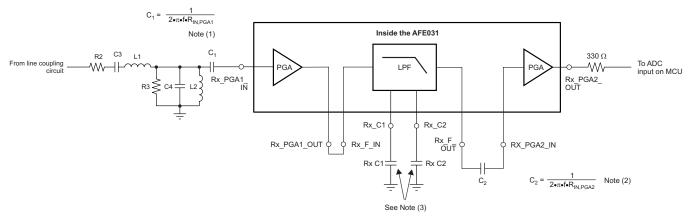

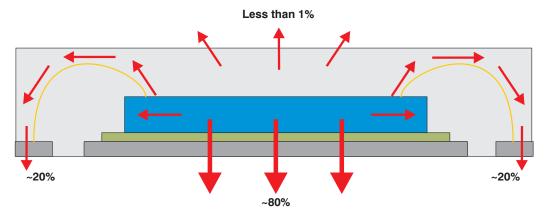

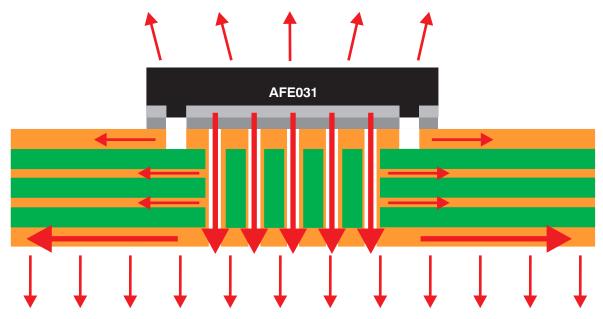

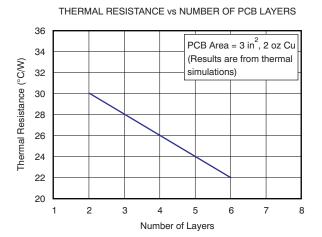

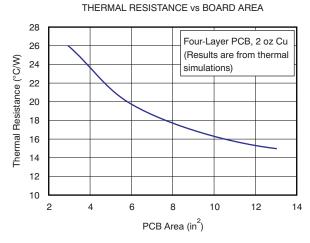

Figure 27. Recommended Tx Signal Chain Connections Using DAC Mode